Current Applied Science and Technology Vol. 22 No. 3 (May-June 2022)

### **Research** article

# **PMMA/High-***k* Self-assembled TiO<sub>2</sub> /**PMMA** Multi-layer Gate Dielectric for P3HT Organic Field Effect Transistors

Kroekchai Inpor<sup>1</sup>, Nongluck Houngkamhang<sup>1\*</sup>, Chanchana Thanachayanont<sup>2</sup>, Seeroong Prichanont<sup>3</sup> and Navaphun Kayunkid<sup>1</sup>

<sup>1</sup>College of Materials Innovation and Technology, King Mongkut's Institute of Technology Ladkrabang, Bangkok, Thailand <sup>2</sup>National Metal and Materials Technology Center, Pathum Thani, Thailand <sup>3</sup>Department of Chemical Engineering, Chulalongkorn University, Bangkok, Thailand

Received: 5 June 2021, Revised: 3 August 2021, Accepted: 15 September 2021

DOI....

### Abstract

| Keywords              | In this work, a multi-layer structure of poly (methyl methacrylate)/<br>titanium dioxide/poly (methyl methacrylate) (PMMA/TiO <sub>2</sub> /PMMA;<br>PTP) was proposed as a top-gate insulator for P3HT-based organic field-                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| organics field-effect | effect transistors (OFETs). Adding a TiO2 interlayer as a high dielectric                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| transistors;          | constant (high- $k$ ) material into PMMA film enables the modification of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| dielectric constant;  | the dielectric constant of the multi-layers PTP film. The content of TiO <sub>2</sub> in the PTP film, which can be varied by changing the number of soaking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TiO <sub>2</sub> ;    | cycles in TiO <sub>2</sub> solution, plays a crucial rule in modifying the dielectric                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| PMMA;                 | constant of the PTP film. The higher the $TiO_2$ content used in the PTP film, the higher the dielectric constant of PTP film can be obtained.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| РЗНТ                  | However, using high TiO <sub>2</sub> content led to a reduction in the dielectric constant of the PTP film due to leakage current induced by the agglomeration of TiO <sub>2</sub> . The utilization of the top-gate insulator containing TiO <sub>2</sub> significantly enhanced several P3HT-OFETs characteristics, e.g., an increase in the $I_{on}/I_{off}$ ratio, and a decrease in the threshold voltage. However, the use of the PTP top-gate insulator with a high content of TiO <sub>2</sub> resulted in regressions in the OFETs characteristics, such as a decrease in carrier mobility and reduction in the $I_{on}/I_{off}$ ratio. |

|                       | OFETs operating at the optimum conditions of the PTP gate-insulator, with PTP thickness of 225 nm and RMS roughness of 20.0 nm, provided a dielectric constant of 7.13, a threshold voltage of -8.49 V, a saturation mobility of $2.2 \times 10^{-4}$ cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> , $I_{on}/I_{off}$ ratio of 37.9, and a subthreshold slope of 0.39 V/decade.                                                                                                                                                                                                                                                               |

<sup>\*</sup>Corresponding author: Tel.: (+66) 2 329 8000 Fax: (+66) 2 329 8265 E-mail: nongluck.ho@kmitl.ac.th

### 1. Introduction

An organic field-effect transistor (OFET) is a field-effect transistor (FET) that uses organic or polymer materials as a semiconducting layer. Such transistors offer several advantages, such as high flexibility and light weight which are suitable for wearable applications. They can be fabricated large-scale via solution processability leading to low manufacturing cost [1-3]. Therefore, OFETs are frequently applied in a wide variety of products such as optoelectronics-based devices, memory devices, and mechanical and chemical sensing and monitoring devices. However, OFETs display certain inefficient electrical characteristics compared to conventional inorganic-based FETs, e.g., low saturation mobility ( $\mu_{sat}$ ), low on/off current ( $I_{on}/I_{off}$ ) ratio, high threshold voltage ( $V_{th}$ ) and low environmental stability. The above-mentioned drawbacks obstruct the use of OFETs in practical applications. Therefore, the enhancement of the electrical properties of OFETs has become an attractive research issue [4-6].

A crucial problem generally found with the utilization of OFETs is the requirement of high  $V_{th}$ . The  $V_{th}$  is defined as the minimum required voltage applied across the gate and source ( $V_{GS}$ ) of OFETs to allow the current flow from drain to source ( $I_{DS}$ ). The  $V_{th}$  is strongly dependent on the ability to generate the number of field-induced carriers per unit area ( $N_c$ ) in the channel at the gate insulator/semiconductor interface. The approximate value of  $N_c$  is given by equation (1).

$$N_c = \frac{k\varepsilon_0}{ed} V_{GS} \tag{1}$$

where, k is a dielectric constant,  $\varepsilon_0$  is the permittivity of a vacuum, d is a thickness of the gate insulator, and e is the charge of an electron. Higher  $k\varepsilon_0$  of the gate insulator requires lower gate potential to generate sufficient carriers to fill the traps. As consequence, OFETs with high-k gate insulator can be operated at lower  $V_{th}$ . Therefore, the use of high-k material as a gate insulator is an approach to reduce the  $V_{th}$  of OFETs [7, 8].

Among the materials used as gate insulators in FETs, metal oxides (MO), e.g., TiO<sub>2</sub> (k = 80), Al<sub>2</sub>O<sub>3</sub> (k = 8), HfO<sub>2</sub> (k = 25) and ZrO<sub>2</sub> (k = 25), are commonly used due to their high dielectric constants compared to conventional SiO<sub>2</sub> gate insulators (k = 3.9) [9]. However, these materials are not suitable for use in OFETs owing to their influence on local morphology and distribution of electronics states at the interface of organic semiconductors, which lead to decrease of the mobility of transistors [10]. Alternative materials used as gate insulators in OFETs, especially in top-gate structures, are polymers, e.g., poly(methyl methacrylate) (PMMA) and poly(4-vinyl phenol) (PVP). Such materials offer several advantages, i.e., low fabrication temperature (< 150°C) which can prevent the degradation of organic semiconducting layer, and less carrier traps generated at the interface between polymeric insulator and organic semiconductor. Nevertheless, the low dielectric constant that is generally observed in polymers leading to an increase of  $V_{th}$ , is a severe limitation on the use of polymers as gate insulators in OFETs. Then, the modification of the dielectric constant of polymers as gate insulators in OFETs.

Several approaches have been proposed to modify the dielectric constant of polymeric gate insulators. First, by adding high-*k* materials into the polymer matrix. In this approach, metal oxide nanoparticles (NPs) such as TiO<sub>2</sub> and SiO<sub>2</sub> are promising candidates. Chen *et al.* [11, 12] reported the significant increase of dielectric constant obtained from composited PVP-TiO<sub>2</sub> film compared to pure PVP film. Moreover, the concentration of TiO<sub>2</sub> in PVP is evidently correlated to the increment of dielectric constant of composited film. However, such approaches possibly encounter a problem with non-uniform distribution of MO NPs in the composite layer. Second, by using double layers composed of high-*k* material and polymer as gate insulators. Yang *et al.* [13, 14] reported a

drastic increase of capacitance obtained from double layers of  $TiO_2$  and PVP films. They noted that the capacitance was directly proportional to the dielectric constant. An increase in capacitance also meant an increase in the dielectric constant. In addition, the increasing capacitance of a double layer gate insulator correlated with the thickness of the  $TiO_2$  layer. Compared to former approaches, the use of gate insulator with stacking layers provided the opportunity to precisely control the uniformity and fine-tuning of the properties of gate insulator.

There are two configurations used to fabricate OFETs; (i) bottom gate structures, and (ii) top-gate structures. Top-gate OFETs have many advantages. For example, the gate pattern and the channel length can be precisely fabricated by conventional photolithographic processes. The gate insulator that covers the organic layer plays an important role as a protecting layer, preventing the degradation of the organic semiconducting layer by the environment. Moreover, this configuration provides a way to modify the properties of gate insulator with external factors, e.g., chemical and biological interactions, which are suitable for the use of OFETs as sensing applications. Therefore, this research work is focused on OFETs prepared with top-gate configuration.

In this work, the insertion of TiO<sub>2</sub> high-*k* material sandwiched between PMMA layers is proposed to enhance the dielectric constant of the gate insulator. The self-assembled monolayer (SAM) method is used to deposit TiO<sub>2</sub> interlayer. The effects of TiO<sub>2</sub> contents on the dielectric constant of the PMMA/SAM-TiO<sub>2</sub>/PMMA (PTP) multi-layers gate insulator was investigated from metal/insulator/metal (MIM) structure. In addition, the OFET characteristics, e.g., saturation mobility,  $I_{onf}/I_{off}$  ratio, and  $V_{th}$ , were characterized from the top-gate OFET using PTP gate stack insulator and poly (3-hexylthiophene-2,5-diyl) (P3HT) as the active layer.

### 2. Materials and Methods

#### **2.1 Materials**

P3HT, PMMA and TiO<sub>2</sub> NPs (P25) were purchased from Sigma-Aldrich. Analytical reagent grade (AR grade) anisole, chloroform and 1,2 dichlorobenzene were used as solvents in this work without further purification. The 100 nm-thick indium tin oxide (ITO) coated on glass slide with a sheet resistance ( $R_s$ ) of 10 ohms/square was purchased from Prazisions glas & optik GmbH.

#### 2.2 Fabrication and characterization of PMMA/SAM-TiO<sub>2</sub>/PMMA gate insulator

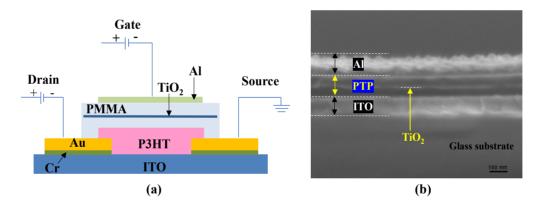

The PTP multi-layered film was used as a gate dielectric of the OFETs. The dielectric properties of the PTP film were analyzed before combining with P3HT semiconducting film. The MIM structure fabricated in this work was captured as a TEM image, as shown in Figure 1(b). The MIM structure was conducted on the ITO coated glass substrate which was used as a bottom electrode. The PMMA layer was fabricated by dissolving 60 mg/ml of PMMA in anisole and spin-coated on ITO substrate using rotation speed at 5500 rpm for 2 min in a glovebox. The samples were dried at 75°C overnight in the glovebox to remove residual solvent. Next, the samples were soaked with TiO<sub>2</sub> NPs dispersed in deionized (DI) water with the concentrations of 10 mg/ml for 30 min to form a TiO<sub>2</sub> layer. After TiO<sub>2</sub> coating, the samples were dried in air ambient for 5 min. To increase the amount of TiO<sub>2</sub> NPs, the soaking of sample in 10 mg/ml of TiO<sub>2</sub> solution was repeated for 2, 4, 6 and 8 cycles. After drying the samples in the glovebox overnight, the top layer of PMMA film was deposited by using the same process condition as the bottom PMMA layer. Finally, PTP multi-layer gate insulator on ITO substrate was obtained. The thickness of the PTP film was investigated via x-ray diffraction (XRD) (Rigaku, TTRAX III). The 100 nm-thick top aluminum electrode with the

dimensions of 0.75x1.925 cm<sup>2</sup> was fabricated on the PTP structure by thermal evaporation method (Edwards 306). The capacitance and dielectric constant versus frequency profiles obtained for each PTP gate insulator with different TiO<sub>2</sub> NPs concentrations were measured by precision impedance analyzer (Agilent 4294a) with a constant AC voltage of 10 mV at room temperature ( $25^{\circ}$ C).

## 2.3 Fabrication and characterization of top-gate OFETs with PMMA/SAM-TiO<sub>2</sub>/PMMA gate insulator

A schematic diagram of top-gate OFET structure with PTP gate insulator is shown in Figure 1(a). An interdigitated pattern of 10 nm-thick chromium (Cr) and 50 nm-thick gold (Au) layers were employed as the source-drain electrode. The channel length (L) and the channel width (W) of OFET device was 20  $\mu$ m and 1673  $\mu$ m, respectively. The P3HT active semiconducting layer was deposited on the source-drain electrode by spin-coating a solution of 12 mg/ml P3HT dissolved in co-solvents of chloroform: 1, 2 dichlorobenzene at 1: 0.5 volume ratio at 3000 rpm for 1 min in the glovebox. Next, the PTP multi-layer gate insulator was deposited on the P3HT layer using the same protocol as described in the previous section. The content of TiO<sub>2</sub> NPs in PTP gate insulator was varied through the repeat of soaking samples in TiO<sub>2</sub> NPs solution for 2, 4, 6 and 8 cycles. The morphology of the PTP multi-layer gate insulator deposited on the P3HT active layer was characterized by atomic force microscope (AFM) (SII Instruments, SPA400). The 70 nm-thick Al film deposited by thermal evaporation was used as a top-gate electrode. Finally, the electrical characteristics of the OFETs were measured by Keithley 6430 and 2420 source meters at room temperature (25°C).

Figure 1. (a) Schematic diagram of top-gate OFETs with Al/PTP/P3HT/Au gate-stack structure and (b) cross-sectional SEM image of Al/PTP/ITO MIM structure

### 3. Results and Discussion

### 3.1 Characteristics of PMMA/TiO<sub>2</sub>/PMMA multi-layers gate insulator

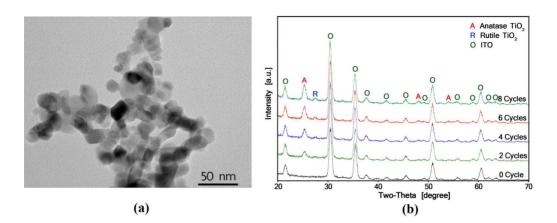

The TEM image in Figure 2(a) shows the morphology and the particle size of TiO<sub>2</sub> NPs which exhibited oval shape and clumped distribution with an approximately dimensional size of 18x23 nm. The X-ray diffraction (XRD) was used to characterize the PTP film coated on ITO substrate to reveal the formation of TiO<sub>2</sub> interlayer. The x-ray diffractograms of the PTP films obtained from different TiO<sub>2</sub> soaking cycles (0 to 8 cycles) are demonstrated in Figure 2(b). The diffracting peaks at 20 angle of 25° and 28° are dominantly observed. These two peaks correspond to the diffraction

**Figure 2.** (a) Transmission electron microscope (TEM) image of TiO<sub>2</sub> nanoparticles used in this work and (b) XRD diffractograms of PMMA/TiO<sub>2</sub>/PMMA films prepared on ITO substrate with different soaking cycles of TiO<sub>2</sub>

of the  $TiO_2$  layer as anatase and rutile phases, respectively. No peak shift was observed on the xray diffractograms obtained from all the PTP films. This suggests that the preparation process of PTP did not affect the formation of the  $TiO_2$  layer. Additionally, the increase in soaking cycles of sample into  $TiO_2$  solution (up to 8 cycles) led to an increase in the intensity of diffracting peaks correlated to  $TiO_2$ . It was indicated that the more soaking cycles were applied, the higher  $TiO_2$ content observed on PTP film.

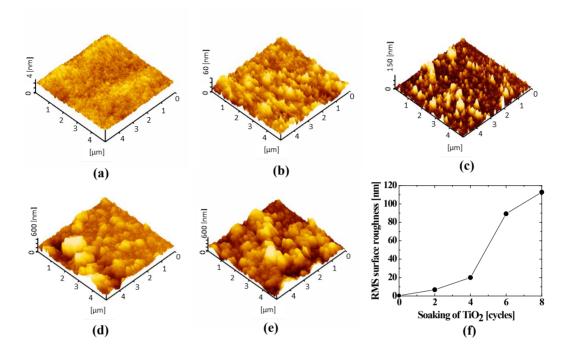

The morphological characteristics of the PTP films prepared by different  $TiO_2$  contents were investigated by AFM. Figures 3(a) to 3(e) illustrate the surface morphology of the PTP films with different  $TiO_2$  soaking cycles (up to 8 cycles). The values of root mean square (RMS) surface roughness obtained from the PTP films as a function of soaking cycles are shown in Figure 3(f) and Table 1. It can be clearly observed that the surface morphology of the PTP film correlated with the content of  $TiO_2$  existing as an interlayer. The PMMA film without  $TiO_2$  interlayer (0 soaking cycle) exhibited smooth surface RMS roughness of 0.4 nm, with small and dense grain. With the existence of  $TiO_2$  interlayer, the surface roughness and grain agglomeration increased. Higher number of  $TiO_2$  soaking cycles of 8 cycles significantly increased the RMS roughness from 0.4 to 112.8 nm.

To investigate the dielectric constant of PTP multi-layers obtained from different TiO<sub>2</sub> contents, MIM structure using PTP as an active layer sandwiched by ITO and Al electrodes was employed. The relative dielectric constant ( $\varepsilon_r$ ) was extracted through the measurement of capacitances obtained from the parallel plate capacitor using equation (2):

$$\varepsilon_r = \frac{c_i}{c_o} = \frac{\varepsilon_o \varepsilon_r A}{d c_o} \tag{2}$$

where  $C_0$  is the capacitance measured with a vacuum between its plates,  $C_i$  is the capacitance, A is the electrode area of the capacitor, and d is the thickness of gate insulator.

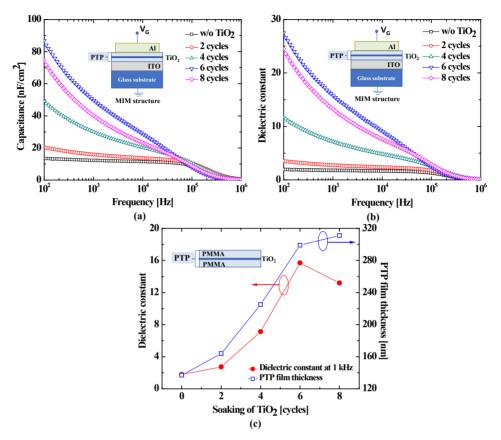

Figure 4(a) shows the capacitance-frequency (C-F) characteristics of PTP multi-layers with different  $TiO_2$  soaking cycles. A significant enhancement of capacitance was clearly observed in the PTP films containing higher  $TiO_2$  content. However, the capacitance was slightly decreased when the  $TiO_2$  soaking cycles had reached 8 cycles. Since the dielectric constant was correlated to not only capacitance but also to the thickness of the dielectric layer, as shown in equation (2), the thickness of the PTP films was measured by step-profilometer. The dielectric constant-frequency

**Figure 3.** The AFM topographic images obtained from (a) PMMA film (without TiO<sub>2</sub>) and PTP films prepared by (b) 2 soaking cycles, (c) 4 soaking cycles, (d) 6 soaking cycles, (e) 8 soaking cycles in TiO<sub>2</sub> solution, and f) the correlation between RMS surface roughness of PTP films and TiO<sub>2</sub> soaking cycles

| Table 1.   | Physical and electrical pro           | perties of the | PMMA/ | TiO <sub>2</sub> /PMMA | multi-layer gat | te insulators |

|------------|---------------------------------------|----------------|-------|------------------------|-----------------|---------------|

| with diffe | erent TiO <sub>2</sub> soaking cycles |                |       |                        |                 |               |

| Soaking of TiO2<br>[cycles] | <i>Ci</i> at 1 kHz<br>[nF/cm <sup>2</sup> ] | Dielectric constant<br>at 1 kHz | PTP film<br>thickness<br>[nm] | RMS surface<br>roughness [nm] |

|-----------------------------|---------------------------------------------|---------------------------------|-------------------------------|-------------------------------|

| 0                           | 16.5                                        | 1.78                            | 137                           | 0.4                           |

| 2                           | 21.3                                        | 2.74                            | 164                           | 6.8                           |

| 4                           | 40.3                                        | 7.13                            | 225                           | 20.0                          |

| 6                           | 66.8                                        | 15.7                            | 299                           | 89.3                          |

| 8                           | 53.8                                        | 13.2                            | 311                           | 112.8                         |

**Figure 4.** (a) The capacitance-frequency and (b) dielectric constant-frequency characteristics of the ITO/PMMA/TiO<sub>2</sub>/PMMA/Al MIM capacitor prepared by varying TiO<sub>2</sub> soaking cycles and (c) the correlation between dielectric constant and the thickness of PTP film as a function of number of TiO<sub>2</sub> soaking cycles

characteristics of each PTP film were calculated using equation (2) and are illustrated in Figure 4(b). In addition, the values of capacitance and dielectric constant at the frequency of 1 kHz as well as the thicknesses of the PTP films are reported in Table 1.

Figure 4(b) shows that all PTP samples exhibited the conventional characteristic between dielectric constant versus applied frequency. The decrease of the dielectric constant at low frequency (40 Hz to 1 kHz) is attributed to the space-charge polarization of the TiO<sub>2</sub> interlayer [15-17]. This polarization is decreased when the dipole rotation fails to keep up with the changes in the applied electric field at higher frequency. The suppression of the dielectric constant at high frequencies (>  $10^4$  Hz) is caused by orientation polarization or dipole polarization. This polarization is produced by permanent electric dipoles in PMMA oriented in the direction of the applied field, which is difficult to rotate at high frequency range [18]. Then, a further decrease in the dielectric constant of the PTP films was observed at high frequency. Interestingly, the increase of the dielectric constant was clearly observed in all samples that contained TiO<sub>2</sub> interlayer. In comparison with the sample without TiO<sub>2</sub> interlayer (0 soaking cycle), the dielectric constant (at 1 kHz) of PTP multi-layer gate insulators with the soaking cycles of 2 to 6 cycles increased from 1.78 to 15.7. The correlation of dielectric constant with TiO<sub>2</sub> soaking cycles and the thickness of PTP films are shown in Figure 4(c). The higher the TiO<sub>2</sub> soaking cycles used to prepare PTP film, the higher the dielectric constant of

PTP films obtained. This result suggested that the enhancement of dielectric constant is attributed to the existence of high-*k* TiO<sub>2</sub> interlayer in the PTP films. However, there was a slightly decrease in dielectric constant observed in the PTP samples prepared by TiO<sub>2</sub> soaking cycles. The declination of dielectric constant in the PTP sample with 8 cycles soaking of TiO<sub>2</sub> solution is possibly explained by (i) an increase of the surface roughness and grain boundaries of PTP film that increases the interface area at a PMMA/TiO<sub>2</sub> interfaces [16] and (ii) the high crystallinity of TiO<sub>2</sub> that existed in PTP film and the surface roughness of PTP film leading to an increase in leakage current between MIM electrodes [19]. The results obtained from AFM and XRD can evidently confirm the significant increase in both surface roughness and crystallinity of the PTP sample prepared by 8 cycles of TiO<sub>2</sub> soaking compared to the other process conditions.

### **3.2 Electrical characteristics of OFETs using PMMA/TiO<sub>2</sub>/PMMA multi-layers gate insulators**

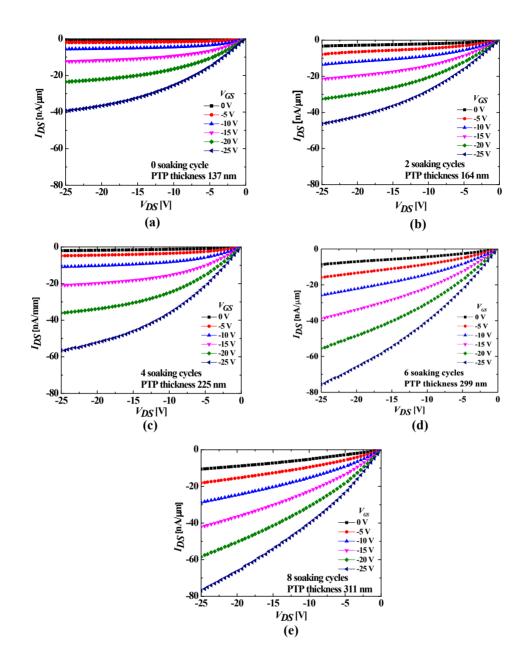

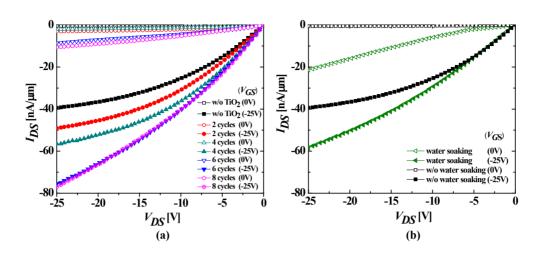

The utilization of PTP multi-layer gate insulators to enhance the characteristics of top-gate OFET devices was investigated. P3HT was employed as a semiconductor layer. The schematic structure of top-gate OFETs studied in this work is shown in Figure 1(a). The  $I_{DS}$ - $V_{DS}$  characteristics of OFETs with different PTP films are shown in Figures 5(a)-5(e). All the OFET devices exhibited transistor characteristics, i.e. the low leakage current taking place between source-drain electrodes without the bias of gate voltage and the increase of source-drain current  $(I_{DS})$  attributed to the increased voltage applied across the gate and source ( $V_{GS}$ ). This result clearly shows that PTP film can be utilized as the gate insulator for OFETs. Moreover, the different preparation conditions of PTP film also had influence on the electrical characteristics of the constructed OFETs. With the  $V_{GS}$  at -25 V, the  $I_{DS}$ was enhanced with the increment of  $TiO_2$  contents in the PTP gate insulator as shown in Figure 6(a). The increase of  $I_{DS}$  was likely due to the increase in the dielectric constant of the PTP films that contained thicker TiO<sub>2</sub> interlayer. The higher dielectric constant resulted in larger charge-carrier accumulation at the P3HT/gate insulator interface leading to the enhancement of current flow from source to drain electrodes. However, the enhancement of  $I_{DS}$  did not take place further in the OFETs using PTP gate insulators with 8 soaking cycles of  $TiO_2$  solution. This behavior resulted from the decrease in the dielectric constant of the PTP gate insulator as shown in Table 1. This might have been caused by charge scattering at the PTP interlayer, which was due to more agglomeration of  $TiO_2$  resulting in decreased mobility and retardation of the  $I_{DS}$  current flow. It has been noted that the slight increase in  $I_{DS}$  at  $V_{GS} = 0$  V, observed in OFETs using PTP films with higher content of TiO<sub>2</sub> can possibly be attributed to the degradation of P3HT film due to exposure to moisture during the preparation of PTP gate insulator [20, 21]. During the preparation of  $TiO_2$  interlayer, the device was directly submersed in TiO<sub>2</sub> aqueous solution. The water molecules possibly penetrated the PMMA layer through the P3HT. This phenomenon is clearly seen with the change of OFET characteristics when it was submersed in water for 4 h, as shown in Figure 6 (b).

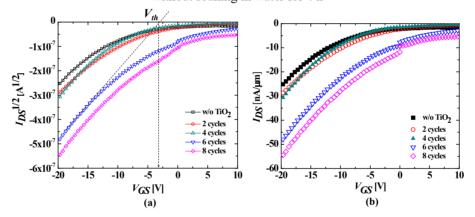

Figure 7 (a) presents the square root of  $I_{DS}$  plotted as a function of  $V_{GS}$  for all OFET devices. From each linear fit in Figure 7 (a), the threshold voltage ( $V_{th}$ ) can be extracted from the x-axis intercept, and subthreshold slope (SS) can be extracted from Figure 7 (b) using inverse slope of the  $I_{DS}$ - $V_{GS}$  plotted. The carrier mobility ( $\mu$ ) is calculated from the saturation regime using the following equation [22]:

$$I_{DS} = \frac{\mu W c_i}{2L} (V_{GS} - V_{th})^2$$

(3)

Where, W and L are the channel width and the channel length of OFETs, respectively. The extracted electrical parameters of the OFETs using different TiO<sub>2</sub> content in PTP gate insulator are summarized in Table 2.

**Figure 5.**  $I_{DS}$ - $V_{DS}$  characteristics of top-gated OFETs with PTP multi-layer gate insulators at the  $V_{GS}$  bias of 0 V to -25 V (a) without (w/o) TiO<sub>2</sub> (0 cycle) and (b) 2, (c) 4, (d) 6, and (e) 8 soaking cycles of TiO<sub>2</sub>

**Figure 6.** (a)  $I_{DS}$ - $V_{DS}$  characteristics of top-gated OFETs with PTP multi-layer gate insulators compared at the  $V_{GS}$  bias of 0 V and -25 V at various TiO<sub>2</sub> soaking cycles and (b)  $I_{DS}$ - $V_{DS}$  characteristic at  $V_{GS}$  bias of 0 V and -25 V of Al/PMMA/PMMA/P3HT/Au OFETs with and without soaking in water for 4 h

**Figure 7.** Transfer characteristics at the  $V_{DS}$  bias of -20 V obtained from OFETs using PTP multilayer gate insulators with 0, 2, 4, 6 and 8 soaking cycles of TiO<sub>2</sub> (a) square root of  $I_{DS}$  plotted as a function of  $V_{GS}$  and (b)  $I_{DS}$  divided by gate length versus  $V_{GS}$

| Soaking cycle of TiO <sub>2</sub><br>[cycles] | Threshold<br>Voltage; V <sub>th</sub><br>[V] | Saturation<br>mobility, $\mu_{sat}$<br>[ $cm^2V^{-1}s^{-1}$ ] | Subthreshold<br>slope; <i>SS</i><br>[V/decade] | Ion/Ioff<br>ratio |

|-----------------------------------------------|----------------------------------------------|---------------------------------------------------------------|------------------------------------------------|-------------------|

| 0                                             | -9.45                                        | 4.7 x 10 <sup>-4</sup>                                        | 0.49                                           | 15.6              |

| 2                                             | -7.72                                        | 3.7 x 10 <sup>-4</sup>                                        | 0.49                                           | 50.4              |

| 4                                             | -8.49                                        | 2.2 x 10 <sup>-4</sup>                                        | 0.40                                           | 37.9              |

| 6                                             | -3.73                                        | 1.2 x 10 <sup>-4</sup>                                        | 0.39                                           | 10.7              |

| 8                                             | -2.89                                        | 1.4 x 10 <sup>-4</sup>                                        | 0.38                                           | 8.5               |

**Table 2.** The extracted electrical parameters of top-gated OFETs using PTP multi-layer gate insulators with different  $TiO_2$  soaking cycles

From Table 2, the subthreshold slope (SS) is defined as  $SS = dV_G/d(\log_{10}I_D)$ . The SS indicates the increase of  $V_G$  required to generate one order of magnitude increase in the  $I_D$ . Typically, a low value of SS is necessary for the device operation with low voltage, high switching speed, and low power consumption. Moreover, low SS also indicate high qualities of gate insulator and interface between semiconductor and insulator. As shown in Figure 7 (b) and Table 2, the OFET device without TiO<sub>2</sub> content in the gate dielectric (zero soaking cycle of TiO<sub>2</sub>) exhibited a large SS of 0.49 V/decade. By using a PTP multi-layer gate insulator with the six soaking cycles of TiO<sub>2</sub>, the SS value was significantly improved to 0.39 V/decade, which is a remarkably low number for polymer-based gate dielectric OFETs. The suppression of SS can be further improved by decreasing the thickness of the PTP multi-layer gate insulator and decreasing RMS surface roughness at the interface between semiconductor and insulator.

It was found that the  $I_{on}/I_{off}$  ratio obtained from OFETs in this work was rather low compared to that obtained from the top-gate OFETs reported in other literature. This possibly resulted from the high off-state leakage current between source and drain electrodes. Hoshino et al. [21] reported that the degradation of P3HT film by moisture led to the enlargement of off-state conduction of P3HT-based OFETs that operated in high moisture atmosphere. In this work, during the fabrication of PTP gate insulator, the devices were submerged in TiO<sub>2</sub> solution for different numbers of cycles. Therefore, the degradation of P3HT possibly took place by moisture penetrating through the PMMA layer. As the result, a high leakage current was observed. However, the  $I_{on}/I_{off}$ ratio of the OFETs increased in the devices contained higher  $TiO_2$  content. This was likely due to the higher on-state current of the OFETs that resulted from larger accumulation of electric charges in the channel from high-k TiO<sub>2</sub> layer. However, at high TiO<sub>2</sub> soaking cycles (6 and 8 cycles), a reduction in the  $I_{on}/I_{off}$  ratio was observed although the dielectric constant of the PTP gate insulator increased. This can be explained by the deterioration of P3HT semiconducting layer during the fabrication of PTP gate insulator. To obtain high TiO<sub>2</sub> content in PTP films, the P3HT layer needs to be immersed in the TiO<sub>2</sub> solution for a longer time. The poor quality of P3HT semiconducting layer cause the increase in off-state current with respect to the on-state current of the OFETs. With the increase in the dielectric constant of PTP insulating layer containing  $TiO_2$  contents, the charge accumulation at the channel is enhanced. Therefore, the gate voltage  $(V_G)$  needed to provide a large enough amount of charge accumulation to allow the  $I_{DS}$  to flow is reduced. The  $V_{th}$ , hence, is sequentially decreased as well.

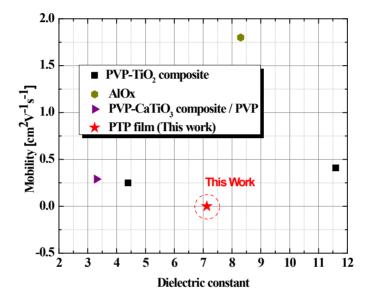

In general, the OFETs studied in the past were bottom-gate structure, where an organic semiconductor was fabricated on top of the dielectric layer. The decrease in mobility corresponded to the increase in surface roughness of the TiO<sub>2</sub> NPs-embedded dielectric layer. However, such mobility degradation depending on the morphology of gate insulator did not occur with the top-gate structure employed in this research since the dielectric layer was fabricated on an organic semiconductor layer. However, there was a slight decrease in mobility observed in the top-gate OFETs using PTP gate insulators with high TiO<sub>2</sub> contents. This was possibly attributable to the nonuniform local charge accumulation induced by the PTP gate insulator with high content of TiO<sub>2</sub>. The agglomeration of TiO<sub>2</sub> that occurred resulted in high surface roughness as well as increase of grain boundary at the interface of PMMA and  $TiO_2$ , which reduced the amorphous nature of  $TiO_2$ gate insulator. This can cause a reduction of the carrier mobility due to the interface trapped charges, electrons or holes, which are trapped at the semiconductor and insulator interface [23]. Moreover, the agglomeration of  $TiO_2$  can cause thickness variation in the PTP film which may lead to leakage current in the device, and then an unstable of  $I_{on}/I_{off}$  ratio is observed with increase of TiO<sub>2</sub> content. The AFM micrographs in Figure 3 show that high TiO<sub>2</sub> content in PTP films leads to increment in surface roughness. The rough surface of the PTP originated from the agglomeration of TiO<sub>2</sub> NPs into large clusters. Therefore, the distribution of local dielectric constant at each domain in the PTP gate insulator is non-uniform. As a consequence, the local charge accumulation at each domain in the conductive channel is also non uniform. As result, the reduction in channel uniformity leads to an increase in resistance in the conducting channel. Then, lower charge mobility takes place in the OFETs. The performance of PMMA/TiO<sub>2</sub>/PMMA (PTP) multi-layer gate insulators compared to the bottom-gate OFETs from others who reported high-k gate insulators is shown in Figure 8. Although the PTP multi-layer gate insulators from this work provided low mobility, a high dielectric constant compared to that of other works was obtained. The OFETs behavior was also obtained by using a PTP gate stack insulator which suggested an alternative way for easy and fast fabrication of high-k -PMMA hybrid material. However, the total thickness of the PTP multi-layer gate insulator and the TiO<sub>2</sub> content should be further investigated to reduce the surface roughness at the semiconductor and insulator interface to improve carrier mobility.

Figure 8. Comparison of the performance of top-gate OFETs with PTP multi-layer gate insulator and the bottom-gate OFETs from other research work

### 4. Conclusions

The utilization of PMMA/TiO<sub>2</sub>/PMMA (PTP) multi-layers as an alternative high-*k* gate insulator for top-gate P3HT-based OFETs film was proposed. The TiO<sub>2</sub> content of the PTP film played a key role in modifying the dielectric constant of the gate insulator. When the optimum content of TiO<sub>2</sub> in the PTP film was used, a high dielectric constant of PTP film was obtained. However, the use of high TiO<sub>2</sub> content and conducting phase led to decrease of the dielectric constant due to leakage current. By applying the PTP film as top-gate insulator, the OFET characteristics were improved, e.g., an increase in  $I_{on}/I_{off}$  ratio and a decrease in threshold voltage were seen. The enhancement of OFET characteristics was attributed to the better induction of charge accumulation by the PTP film containing TiO<sub>2</sub> interlayer. However, the degradations in OFET performance, e.g., the reduction in  $I_{on}/I_{off}$  ratio and the slight decrease in mobility were observed in devices that used PTP gate insulators with high TiO<sub>2</sub> contents. The degradation of OFET characteristics corresponded to (i) the deterioration of P3HT by moisture during the fabrication of the PTP gate insulator and (ii) the nonuniform local charge accumulation that resulted from the agglomeration of TiO<sub>2</sub> in the PTP gate insulator.

### 5. Acknowledgements

The authors would like to thank Innovative Nanocoating Research Team, National NanoTechnology Center (NANOTEC), Thailand for OFETs fabrication

### References

- Torsi, L., Dodabalapur, A., Rothberg, L.J., Fung A.W.P. and Katz, H.E., 1996. Intrinsic transport properties and performance limits of organic field-effect transistors. *Science*, 272, 1462-1464.

- [2] Koutsiakia, C., Kaimakamisa, T., Zachariadisa, A., Papamichaila, A., Kamarakia, C., Fachourib S., Gravalidisa, C., Laskarakisa, A. and Logothetidisa, S., 2019. Efficient combination of roll-to-roll compatible techniques towards the large area deposition of a polymer dielectric film and the solution-processing of an organic semiconductor for the fieldeffect transistors fabrication on plastic substrate. *Organic Electronics*, 73, 231-239.

- [3] Zschieschang, U., Ante, F., Yamamoto, T., Takimiya, K., Kuwabara, H., Ikeda, M., Sekitani, T., Someya, T., Kern, K. and Klauk, H., 2010. Flexible low-voltage organic transistors and circuit based on a high-mobility organic semiconductor with good air stability. *Advanced Materials*, 22, 982-985.

- [4] Ismail, L.N., Samsul, S., Musa, M.Z. and Norsabrina, S., 2018. Fabrication of p-type organic field effect transistor using PMMA:TiO<sub>2</sub> as nanocomposite dielectric layer. *IOP Conference Series: Materials Science and Engineering*, 340(1), 012005, https://doi.org/10.1088/1757-899X/340/1/012005.

- [5] Deman, A.L. and Tardy, J., 2006. Stability of pentacene organic field effect transistors with a low-k polymer/high-k oxide two-layer gate dielectric. *Materials Science and Engineering: C*, 26, 421-426.

- [6] Noh, Y.-Y. and Sirringhaus, H., 2009. Ultra-thin polymer gate dielectrics for top-gate polymer field effect transistors. *Organic Electronics*, 10, 174-180.

- [7] Facchetti, A., Yoon, M. and Marks, T.J., 2005. Gate dielectrics for organic field effect transistors: new opportunities for organic electronics. *Advanced Materials*, 17, 1705-1725.

- [8] Herlogsson, L., Crispin, X., Robinson, N.D., Sandberg, M., Hagel, O., Gustafsson, G. and Berggren, M., 2007. Low-voltage polymer field-effect transistors gated via a proton conductor. *Advanced Materials*, 19, 97-101.

- [9] Yim, K., Yong, Y., Lee, J., Lee, K., Nahm, H.H., Yoo, J., Lee, C., Hwang, C.S. and Han, S., 2015. Novel high-κ dielectrics for next-generation electronic devices screened by automated ab initio calculations. NPG Asia Materials, 7(6), e190, https://doi.org/10.1038/am.2015.57.

- [10] Veres, J., Ogier, S. and Lloyd, G., 2004. Gate insulator in organic field-effect transistors. *Chemistry of Materials*, 16, 4543-4555.

- [11] Chen, F., Chu, C., He, J., Yang, Y. and Lin, J., 2004. Organic thin-film transistors with nanocomposite dielectric gate insulator. *Applied Physics Letters*, 85, 3295-3297.

- [12] Chen, F., Chuang, C., Lin, Y., Kung, L., Chen, T. and Shieh, H. D., 2006. Low-voltage organic thin-film transistors with polymeric nanocomposite dielectrics. *Organic Electronics*, 7, 435-439.

- [13] Yang, F., Chang, K., Hsu, M. and Liu, C., 2008. Low-operative-voltage polymer transistor with solution processed low-k polymer/high-k metal-oxide bilayer insulators. *Organic Electronics*, 9, 925-929.

- [14] Yang, F., Hsu, M., Hwang, G. and Chang, K., 2010. High-performance poly(3hexylthiophene) top-gate transistors incorporating TiO<sub>2</sub> nanocomposite dielectrics. *Organic Electronics*, 11, 81-88.

- [15] Wypych, A., Bobowska, I., Tracz, M., Opasinska, A., Kadlubowski, S., Krzywania-Kaliszewska, A., Grobelny, J. and Wojciechowski, P., 2014. Dielectric properties and characterization of titanium dioxide obtained by different chemistry methods. *Journal of Nanomaterials*, 2014, https://doi.org/10.1155/2014/124814.

- [16] Feng, Y., Yin, J., Chen, M., Song, M., Su, B. and Lei, Q., 2013. Effect of nano-TiO<sub>2</sub> on the polarization process of polyimide-TiO<sub>2</sub> composites. *Materials Letters*, 96, 113-116.

- [17] Abouelhassan, S., 2010. Investigation of the dielectric properties and thermodynamic parameters of (50 – x) P<sub>2</sub>O<sub>5</sub> -xAgI -40Ag<sub>2</sub>O -10Fe<sub>2</sub>O<sub>3</sub> ionic glass. *Chinese Journal of Physics*, 48, 650-661.

- [18] Harun, M. H., Saion, E., Kassim, A., Mahmud, E., Hussain, M. Y. and Mustafa, I. S., 2009. Dielectric Properties of Poly (vinyl alcohol)/polypyrrole composite polymer films. *Journal for the Advancement of Science & Arts*, 1, 9-16.

- [19] Sung, S., Park, S., Lee, W., Son, J., Kim, C. and Yoon, M., 2015. Low-voltage flexible organic electronics based on high performance sol-gel titanium dioxide dielectric. ACS Applied Materials & Interfaces, 7, 7456-7461.

- [20] Hoshino, S., Yoshida, M., Uemura, S., Kodzasa, T., Takada, N., Kamata, T. and Yase, K., 2004. Influence of moisture on device characteristics of polythiophene-based field-effect transistors. *Journal of Applied Physics*, 95, 5088-5093.

- [21] Chabinyc, M.L., Endicott, F., Vogt, B.D., DeLongchamp, D.M., Lin, E.K., Wu, Y., Liu, P. and Ong, B.S., 2006. Effects of humidity on unencapsulated poly(thiophene) thin-film transistors. *Applied Physics Letters*, 88(11), 113514, https://doi.org/10.1063/1.2181206.

- [22] Horowitz, G., Hajlaoui, R., Bouchriha, Bourguiga, H.R. and Hajlaoui, M., 1998. The concept of "Threshold-Voltage" in organic field-effect transistors. *Advanced Materials*, 10, 923-927.

- [23] Ismail, L.N., Zulkefle, H., Sauki, N.S.A.M., Zain, A., Herman, S.H. and Mahmood, M.R., 2013. Characterization of metal-insulator-semiconductor capacitor with poly(methyl methacrylate): titanium dioxide as insulator. *Japanese Journal of Applied Physics*, 52(6S), https://doi.org/10.7567/JJAP.52.06GG02.

- [24] Qi, M., Zheng, C., Shuming, D., Xiaotao, Z., Xiaochen, R., and Wenping, H., 2020. A lowtemperature solution-process high-k dielectric for high-performance flexible organic fieldeffect transistors. *Frontiers in Materials*, 7, https://doi.org/10.3389/fmats.2020.570002.

- [25] Xiong, C., Hoa, Z., Yu, Z., Xiangfeng, G., Zitong, Z. and Dagui, C., 2020. Low-power flexible organic field-effect transistors with solution-processable polymer-ceramic nanoparticle composite dielectrics. *Nanomaterials*, 10, 518, https://doi.org/10.3390/nano10030518.